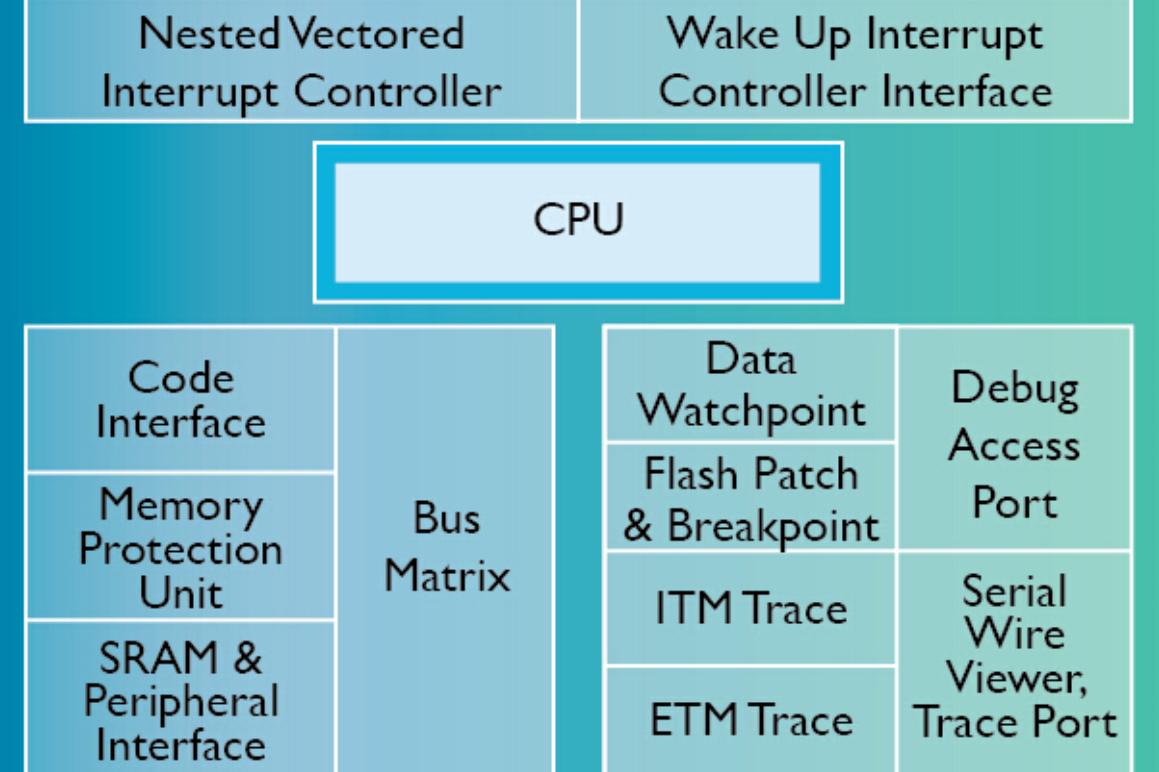

概述

Cortex-M3是一個32位處理器内核。内部的數據路徑是32位的,寄存器是32位的,存儲器接口也是32位的。CM3采用了哈佛結構,擁有獨立的指令總線和數據總線,可以讓取指與數據訪問并行不悖。這樣一來數據訪問不再占用指令總線,從而提升了性能。為實現這個特性,CM3内部含有好幾條總線接口,每條都為自己的應用場合優化過,并且它們可以并行工作。但是另一方面,指令總線和數據總線共享同一個存儲器空間(一個統一的存儲器系統)。換句話說,不是因為有兩條總線,可尋址空間就變成8GB了。

比較複雜的應用可能需要更多的存儲系統功能,為此CM3提供一個可選的MPU,而且在需要的情況下也可以使用外部的cache。另外在CM3中,Both小端模式和大端模式都是支持的。

CM3内部還附贈了好多調試組件,用于在硬件水平上支持調試操作,如指令斷點,數據觀察點等。另外,為支持更高級的調試,還有其它可選組件,包括指令跟蹤和多種類型的調試接口。

内核架構

ARMCortex-M3采用哈佛結構,并選擇了适合于微控制器應用的三級流水線,但增加了分支預測功能。

現代處理器大多采用指令預取和流水線技術,以提高處理器的指令執行速度。流水線處理器在正常執行指令時,如果碰到分支(跳轉)指令,由于指令執行的順序可能會發生變化,指令預取隊列和流水線中的部分指令就可能作廢,而需要從新的地址重新取指、執行,這樣就會使流水線“斷流”,處理器性能因此而受到影響。特别是現代C語言程序,經編譯器優化生成的目标代碼中,分支指令所占的比例可達10-20%,對流水線處理器的影響會的更大。為此,現代高性能流水線處理器中一般都加入了分支預測部件,就是在處理器從存儲器預取指令時,當遇到分支(跳轉)指令時,能自動預測跳轉是否會發生,再從預測的方向進行取指,從而提供給流水線連續的指令流,流水線就可以不斷地執行有效指令,保證了其性能的發揮。

ARMCortex-M3内核的預取部件具有分支預測功能,可以預取分支目标地址的指令,使分支延遲減少到一個時鐘周期。

針對業界對ARM處理器中斷響應的問題,Cortex-M3首次在内核上集成了嵌套向量中斷控制器(NVIC)。Cortex-M3的中斷延遲隻有12個時鐘周期(ARM7需要24-42個周期);Cortex-M3還使用尾鍊技術,使得背靠背(back-to-back)中斷的響應隻需要6個時鐘周期(ARM7需要大于30個周期)。Cortex-M3采用了基于棧的異常模式,使得芯片初始化的封裝更為簡單。

Cortex-M3加入了類似于8位處理器的内核低功耗模式,支持3種功耗管理模式:通過一條指令立即睡眠;異常/中斷退出時睡眠;深度睡眠。使整個芯片的功耗控制更為有效。

特點

高性能

許多指令都是單周期的——包括乘法相關指令。并且從整體性能上,Cortex-M3比得過絕大多數其它的架構。

指令總線和數據總線被分開,取值和訪内可以并行不悖

Thumb-2的到來告别了狀态切換的舊世代,再也不需要花時間來切換于32位ARM狀态和16位Thumb狀态之間了。這簡化了軟件開發和代碼維護,使産品面市更快。

Thumb-2指令集為編程帶來了更多的靈活性。許多數據操作現在能用更短的代碼搞定,這意味着Cortex-M3的代碼密度更高,也就對存儲器的需求更少。

取指都按32位處理。同一周期最多可以取出兩條指令,留下了更多的帶寬給數據傳輸。

Cortex-M3的設計允許單片機高頻運行(現代半導體制造技術能保證100MHz以上的速度)。即使在相同的速度下運行,CM3的每指令周期數(CPI)也更低,于是同樣的MHz下可以做更多的工作;另一方面,也使同一個應用在CM3上需要更低的主頻。

2.11.2 先進的中斷處理功能

内建的嵌套向量中斷控制器支持多達240條外部中斷輸入。向量化的中斷功能劇烈地縮短了中斷延遲,因為不再需要軟件去判斷中斷源。中斷的嵌套也是在硬件水平上實現的,不需要軟件代碼來實現。

Cortex-M3在進入異常服務例程時,自動壓棧了R0-R3, R12, LR, PSR和PC,并且在返回時自動彈出它們,這多清爽!既加速了中斷的響應,也再不需要彙編語言代碼了(第8章有詳述)。

NVIC支持對每一路中斷設置不同的優先級,使得中斷管理極富彈性。最粗線條的實現也至少要支持8級優先級,而且還能動态地被修改。

優化中斷響應還有兩招,它們分别是“咬尾中斷機制”和“晚到中斷機制”。

有些需要較多周期才能執行完的指令,是可以被中斷-繼續的——就好比它們是一串指令一樣。這些指令包括加載多個寄存器(LDM),存儲多個寄存器(STM),多個寄存器參與的PUSH,以及多個寄存器參與的POP。

除非系統被徹底地鎖定,NMI(不可屏蔽中斷)會在收到請求的第一時間予以響應。對于很多安全-關鍵(safety-critical)的應用,NMI都是必不不可少的(如化學反應即将失控時的緊急停機)。

低功耗

Cortex-M3需要的邏輯門數少,所以先天就适合低功耗要求的應用(功率低于0.19mW/MHz)在内核水平上支持節能模式(SLEEPING和SLEEPDEEP位)。通過使用“等待中斷指令(WFI)”和“等待事件指令(WFE)”,内核可以進入睡眠模式,并且以不同的方式喚醒。另外,模塊的時鐘是盡可能地分開供應的,所以在睡眠時可以把CM3的大多數“官能團”給停掉。

CM3的設計是全靜态的、同步的、可綜合的。任何低功耗的或是标準的半導體工藝均可放心飲用。

系統特性

系統支持“位尋址帶”操作(8051位尋址機制的“威力大幅加強版”),字節不變的大端模式,并且支持非對齊的數據訪問。

擁有先進的fault處理機制,支持多種類型的異常和faults,使故障診斷更容易。

通過引入banked堆棧指針機制,把系統程序使用的堆棧和用戶程序使用的堆棧劃清界線。如果再配上可選的MPU,處理器就能徹底滿足對軟件健壯性和可靠性有嚴格要求的應用。

調試支持

在支持傳統的JTAG基礎上,還支持更新更好的串行線調試接口。

基于CoreSight調試解決方案,使得處理器哪怕是在運行時,也能訪問處理器狀态和存儲器内容。

内建了對多達6個斷點和4個數據觀察點的支持。

可以選配一個ETM,用于指令跟蹤。數據的跟蹤可以使用DWT

在調試方面還加入了以下的新特性,包括fault狀态寄存器,新的fault異常,以及閃存修補 (patch)操作,使得調試大幅簡化。

可選ITM模塊,測試代碼可以通過它輸出調試信息,而且“拎包即可入住”般地方便使用。

編程模式

Cortex-M3處理器采用ARMv7-M架構,它包括所有的16位Thumb指令集和基本的32位Thumb-2指令集架構,Cortex-M3處理器不能執行ARM指令集。

Thumb-2在Thumb指令集架構(ISA)上進行了大量的改進,它與Thumb相比,具有更高的代碼密度并提供16/32位指令的更高性能。

關于工作模式

Cortex-M3處理器支持2種工作模式:線程模式和處理模式。在複位時處理器進入“線程模式”,異常返回時也會進入該模式,特權和用戶(非特權)模式代碼能夠在“線程模式”下運行。

出現異常模式時處理器進入“處理模式”,在處理模式下,所有代碼都是特權訪問的。

關于工作狀态

Cortex-M3處理器有2種工作狀态。

Thumb狀态:這是16位和32位“半字對齊”的Thumb和Thumb-2指令的執行狀态。

調試狀态:處理器停止并進行調試,進入該狀态。

開發工具

Keil ULINK仿真器

IAR JLink仿真器

對客戶來說用什麼技術、芯片不是主要的。主要的是能否滿足要求。高性價比、開發門檻底、易于使用才是硬道理。Cortex M3從理論上來說是高性價比。但目前已有的芯片的功能太少。Cortex M系列在處理能力基本與ARM7同,主要是成本低,功耗小。

産品構造

synchronous serial 總線

完全可編程的16C550-型 UART

兩個獨立的模拟比較器

可配置為輸出來驅動一個輸出引腳,或産生一個中斷

可在外部輸入引腳或外部輸入引腳和内部參考電壓之間比較

2到18個GPIO 這取決于用戶的配置

在所有的引腳上具有可編程的GPIO中斷,可以邊沿觸發或電平觸發

可編程的GPIO 襯墊配置:

弱上拉或下拉電阻

2 mA, 4 mA, and 8 mA 襯墊驅動

8 mA驅動斜率控制

開漏使能

數字輸入使能

片内LDO電壓調整器

處理器低功率選項:睡眠模式和深度睡眠模式

外設低功率選項:軟件控制關閉個别外設

用戶使能的LDO 未調整電壓檢測和自動複位

通過中斷或複位方式檢測并報告3.3 V 電源電壓下降

IEEE 1149.1-1990 兼容的TAP控制器

經過 JTAG 或串行線調試

28腳SOIC

商業或工業級工作溫度

LM3S316 比 LM3S101 的增強如下:

25 MHz下工作

8級優先級的24個中斷通道

16 kB 的單周期flash存儲器,在2 kB塊的基礎上提供2種形式的flash保護。

4 kB 的單周期SRAM存儲器

4 通道 10-bit ADC 250K采樣/秒

片内溫度傳感器

4個專用的電機控制PWM 輸出

I2C 主從收發 傳輸速度100 kbps标準模式 400 kbps高速模式

3到32個GPIO 這取決于用戶的配置

48腳SOIC