定義

UART是一種通用串行數據總線,用于異步通信。該總線雙向通信,可以實現全雙工傳輸和接收。在嵌入式設計中,UART用來主機與輔助設備通信,如汽車音響與外接AP之間的通信,與PC機通信包括與監控調試器和其它器件,如EEPROM通信。

功能

計算機内部采用并行數據,不能直接把數據發到Modem,必須經過UART整理才能進行異步傳輸,其過程為:CPU先把準備寫入串行設備的數據放到UART的寄存器(臨時内存塊)中,再通過FIFO(FirstInput First Output,先入先出隊列)傳送到串行設備,若是沒有FIFO,信息将變得雜亂無章,不可能傳送到Modem。

它是用于控制計算機與串行設備的芯片。有一點要注意的是,它提供了RS-232C數據終端設備接口,這樣計算機就可以和調制解調器或其它使用RS-232C接口的串行設備通信了。作為接口的一部分,UART還提供以下功能:将由計算機内部傳送過來的并行數據轉換為輸出的串行數據流。

将計算機外部來的串行數據轉換為字節,供計算機内部并行數據的器件使用。在輸出的串行數據流中加入奇偶校驗位,并對從外部接收的數據流進行奇偶校驗。在輸出數據流中加入啟停标記,并從接收數據流中删除啟停标記。處理由鍵盤或鼠标發出的中斷信号(鍵盤和鼠标也是串行設備)。可以處理計算機與外部串行設備的同步管理問題。有一些比較高檔的UART還提供輸入輸出數據的緩沖區,比較新的UART是16550,它可以在計算機需要處理數據前在其緩沖區内存儲16字節數據,而通常的UART是8250。如果您購買一個内置的調制解調器,此調制解調器内部通常就會有16550UART。

通信協議

UART作為異步串口通信協議的一種,工作原理是将傳輸數據的每個字符一位接一位地傳輸。

其中各位的意義如下:

起始位:先發出一個邏輯”0”的信号,表示傳輸字符的開始。

資料位:緊接着起始位之後。資料位的個數可以是4、5、6、7、8等,構成一個字符。通常采用ASCII碼。從最低位開始傳送,靠時鐘定位。

奇偶校驗位:資料位加上這一位後,使得“1”的位數應為偶數(偶校驗)或奇數(奇校驗),以此來校驗資料傳送的正确性。

停止位:它是一個字符數據的結束标志。可以是1位、1.5位、2位的高電平。由于數據是在傳輸線上定時的,并且每一個設備有其自己的時鐘,很可能在通信中兩台設備間出現了小小的不同步。因此停止位不僅僅是表示傳輸的結束,并且提供計算機校正時鐘同步的機會。适用于停止位的位數越多,不同時鐘同步的容忍程度越大,但是數據傳輸率同時也越慢。

空閑位:處于邏輯“1”狀态,表示當前線路上沒有資料傳送。

波特率:是衡量資料傳送速率的指标。表示每秒鐘傳送的符号數(symbol)。一個符号代表的信息量(比特數)與符号的階數有關。例如資料傳送速率為120字符/秒,傳輸使用256階符号,每個符号代表8bit,則波特率就是120baud,比特率是120*8=960bit/s。這兩者的概念很容易搞錯。

基本結構

⑴輸出緩沖寄存器,它接收CPU從數據總線上送來的并行數據,并加以保存。

⑵輸出移位寄存器,它接收從輸出緩沖器送來的并行數據,以發送時鐘的速率把數據逐位移出,即将并行數據轉換為串行數據輸出。

⑶輸入移位寄存器,它以接收時鐘的速率把出現在串行數據輸入線上的數據逐位移入,當數據裝滿後,并行送往輸入緩沖寄存器,即将串行數據轉換成并行數據。

⑷輸入緩沖寄存器,它從輸入移位寄存器中接收并行數據,然後由CPU取走。

⑸控制寄存器,它接收CPU送來的控制字,由控制字的内容,決定通信時的傳輸方式以及數據格式等。例如采用異步方式還是同步方式,數據字符的位數,有無奇偶校驗,是奇校驗還是偶校驗,停止位的位數等參數。

⑹狀态寄存器。狀态寄存器中存放着接口的各種狀态信息,例如輸出緩沖區是否空,輸入字符是否準備好等。在通信過程中,當符合某種狀态時,接口中的狀态檢測邏輯将狀态寄存器的相應位置“1”,以便讓CPU查詢。

設計思想

數據發送的思想是,當啟動字節發送時,通過TxD先發起始位,然後發數據位和奇偶數效驗位,最後再發停止位,發送過程由發送狀态機控制,每次中斷隻發送1個位,經過若幹個定時中斷完成1個字節幀的發送。

數據接收的思想是,當不在字節幀接收過程時,每次定時中斷以3倍的波特率監視RxD的狀态,當其連續3次采樣電平依次為1、0、0時,就認為檢測到了起始位,則開始啟動一次字節幀接收,字節幀接收過程由接收狀态機控制,每次中斷隻接收1個位,經過若幹個定時中斷完成1個字節幀的接收。

為了提高串口的性能,在發送和接收上都實現了FIFO功能,提高通信的實時性。FIFO的長度可以進行自由定義,适應用戶的不同需要。

波特率的計算按照計算公式進行,在設置最高波特率時一定要考慮模拟串口程序代碼的執行時間,該定時時間必須大于模拟串口的程序的規定時間。單片機的執行速度越快,則可以實現更高的串口通訊速度。

工作原理

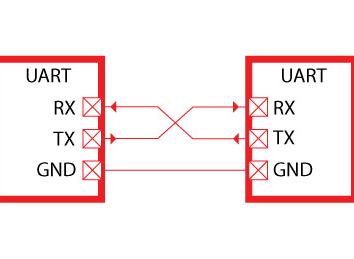

發送接收

發送邏輯對從發送FIFO讀取的數據執行“并→串”轉換。控制邏輯輸出起始位在先的串行位流,并且根據控制寄存器中已編程的配置,後面緊跟着數據位(注意:最低位LSB先輸出)、奇偶校驗位和停止位。

在檢測到一個有效的起始脈沖後,接收邏輯對接收到的位流執行“串→并”轉換。此外還會對溢出錯誤、奇偶校驗錯誤、幀錯誤和線中止(line-break)錯誤進行檢測,并将檢測到的狀态附加到被寫入接收FIFO的數據中。

波特率

波特率除數(baud-ratedivisor)是一個22位數,它由16位整數和6位小數組成。波特率發生器使用這兩個值組成的數字來決定位周期。通過帶有小數波特率的除法器,在足夠高的系統時鐘速率下,UART可以産生所有标準的波特率,而誤差很小。

數據收發

發送時,數據被寫入發送FIFO。如果UART被使能,則會按照預先設置好的參數(波特率、數據位、停止位、校驗位等)開始發送數據,一直到發送FIFO中沒有數據。一旦向發送FIFO寫數據(如果FIFO未空),UART的忙标志位BUSY就有效,并且在發送數據期間一直保持有效。BUSY位僅在發送FIFO為空,且已從移位寄存器發送最後一個字符,包括停止位時才變無效。即UART不再使能,它也可以指示忙狀态。BUSY位的相關庫函數是UARTBusy()

在UART接收器空閑時,如果數據輸入變成“低電平”,即接收到了起始位,則接收計數器開始運行,并且數據在Baud16的第8個周期被采樣。如果Rx在Baud16的第8周期仍然為低電平,則起始位有效,否則會被認為是錯誤的起始位并将其忽略。

如果起始位有效,則根據數據字符被編程的長度,在Baud16的每第16個周期對連續的數據位(即一個位周期之後)進行采樣。如果奇偶校驗模式使能,則還會檢測奇偶校驗位。

最後,如果Rx為高電平,則有效的停止位被确認,否則發生幀錯誤。當接收到一個完整的字符時,将數據存放在接收FIFO中。

中斷控制

出現以下情況時,可使UART産生中斷:

FIFO溢出錯誤

線中止錯誤(line-break,即Rx信号一直為0的狀态,包括校驗位和停止位在内)

奇偶校驗錯誤

幀錯誤(停止位不為1)

接收超時(接收FIFO已有數據但未滿,而後續數據長時間不來)

發送

接收

由于所有中斷事件在發送到中斷控制器之前會一起進行“或運算”操作,所以任意時刻UART隻能向中斷産生一個中斷請求。通過查詢中斷狀态函數UARTIntStatus(),軟件可以在同一個中斷服務函數裡處理多個中斷事件(多個并列的if語句)。

FIFO操作

FIFO是“First-InFirst-Out”的縮寫,意為“先進先出”,是一種常見的隊列操作。Stellaris系列ARM的UART模塊包含有2個16字節的FIFO:一個用于發送,另一個用于接收。可以将兩個FIFO分别配置為以不同深度觸發中斷。可供選擇的配置包括:1/8、1/4、1/2、3/4和7/8深度。例如,如果接收FIFO選擇1/4,則在UART接收到4個數據時産生接收中斷。

發送FIFO的基本工作過程:隻要有數據填充到發送FIFO裡,就會立即啟動發送過程。由于發送本身是個相對緩慢的過程,因此在發送的同時其它需要發送的數據還可以繼續填充到發送FIFO裡。當發送FIFO被填滿時就不能再繼續填充了,否則會造成數據丢失,此時隻能等待。這個等待并不會很久,以9600的波特率為例,等待出現一個空位的時間在1ms上下。發送FIFO會按照填入數據的先後順序把數據一個個發送出去,直到發送FIFO全空時為止。已發送完畢的數據會被自動清除,在發送FIFO裡同時會多出一個空位。

接收FIFO的基本工作過程:當硬件邏輯接收到數據時,就會往接收FIFO裡填充接收到的數據。程序應當及時取走這些數據,數據被取走也是在接收FIFO裡被自動删除的過程,因此在接收FIFO裡同時會多出一個空位。如果在接收FIFO裡的數據未被及時取走而造成接收FIFO已滿,則以後再接收到數據時因無空位可以填充而造成數據丢失。

收發FIFO主要是為了解決UART收發中斷過于頻繁而導緻CPU效率不高的問題而引入的。在進行UART通信時,中斷方式比輪詢方式要簡便且效率高。但是,如果沒有收發FIFO,則每收發一個數據都要中斷處理一次,效率仍然不夠高。如果有了收發FIFO,則可以在連續收發若幹個數據(可多至14個)後才産生一次中斷然後一并處理,這就大大提高了收發效率。

完全不必要擔心FIFO機制可能帶來的數據丢失或得不到及時處理的問題,因為它已經幫你想到了收發過程中存在的任何問題,隻要在初始化配置UART後,就可以放心收發了,FIFO和中斷例程會自動搞定一切。

回環操作

UART可以進入一個内部回環(Loopback)模式,用于診斷或調試。在回環模式下,從Tx上發送的數據将被Rx輸入端接收。

串行協議

在某些Stellaris系列ARM芯片裡,UART還包含一個IrDA串行紅外(SIR)編碼器/解碼器模塊。IrDASIR模塊的作用是在異步UART數據流和半雙工串行SIR接口之間進行轉換。片上不會執行任何模拟處理操作。SIR模塊的任務就是要給UART提供一個數字編碼輸出和一個解碼輸入。UART信号管腳可以和一個紅外收發器連接以實現IrDASIR物理層連接。

通信速度

數據傳輸可以首先從最低有效位(LSB)開始。然而,有些UART允許靈活選擇先發送最低有效位或最高有效位(MSB)。

微控制器中的UART傳送數據的速度範圍為每秒幾百位到1.5Mb。例如,嵌入在ElanSC520微控制器中的高速UART通信的速度可以高達1.152Mbps。UART波特率還受發送和接收線對距離(線長度)的影響。

市場上有隻支持異步通信和同時支持異步與同步通信的兩種硬件可用于UART。前者就是UART名字本身的含義,在摩托羅拉微控制器中被稱為串行通信接口(SCI);Microchip微控制器中的通用同步異步收發器(USART)和在富士通微控制器中的UART是後者的兩個典型例子。

運用

通信領域

UART首先将接收到的并行數據轉換成串行數據來傳輸。消息幀從一個低位起始位開始,後面是5~8個數據位,一個可用的奇偶位和一個或幾個高位停止位。接收器發現開始位時它就知道數據準備發送,并嘗試與發送器時鐘頻率同步。如果選擇了奇偶,UART就在數據位後面加上奇偶位。奇偶位可用來幫助錯誤校驗。

在接收過程中,UART從消息幀中去掉起始位和結束位,對進來的字節進行奇偶校驗,并将數據字節從串行轉換成并行。UART也産生額外的信号來指示發送和接收的狀态。例如,如果産生一個奇偶錯誤,UART就置位奇偶标志。奇偶校驗位适用于檢驗傳輸是否正确的。

計算機

UART是計算機中串行通信端口的關鍵部分。在計算機中,UART相連于産生兼容RS232規範信号的電路。RS232标準定義邏輯“1”信号相對于地為-3到-15伏,而邏輯“0”相對于地為+3到+15伏。所以,當一個微控制器中的UART相連于PC時,它需要一個RS232驅動器來轉換電平。

Uart這裡指的是TTL電平的串口;RS232指的是RS232電平的串口。

TTL電平是5V的,而RS232是負邏輯電平,它定義+5~+12V為低電平,而-12~-5V為高電平。

Uart串口的RXD、TXD等一般直接與處理器芯片的引腳相連,而RS232串口的RXD、TXD等一般需要經過電平轉換(通常由Max232等芯片進行電平轉換)才能接到處理器芯片的引腳上,否則這麼高的電壓很可能會把芯片燒壞。

我們平時所用的電腦的串口就是RS232的,當我們在做電路工作時,應該注意下外設的串口是Uart類型的還是RS232類型的,如果不匹配,應當找個轉換線(通常這根轉換線内有塊類似于Max232的芯片做電平轉換工作的),可不能盲目地将兩串口相連。